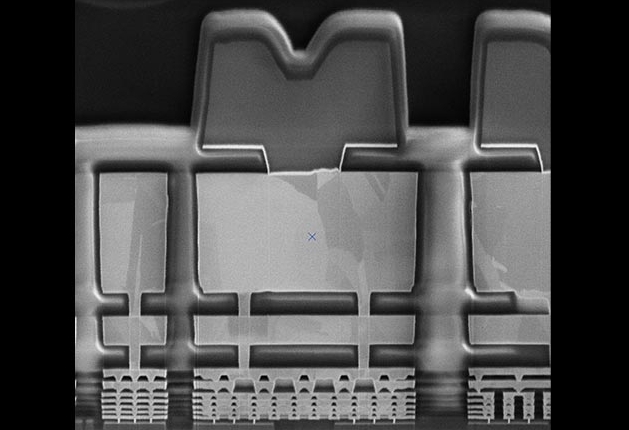

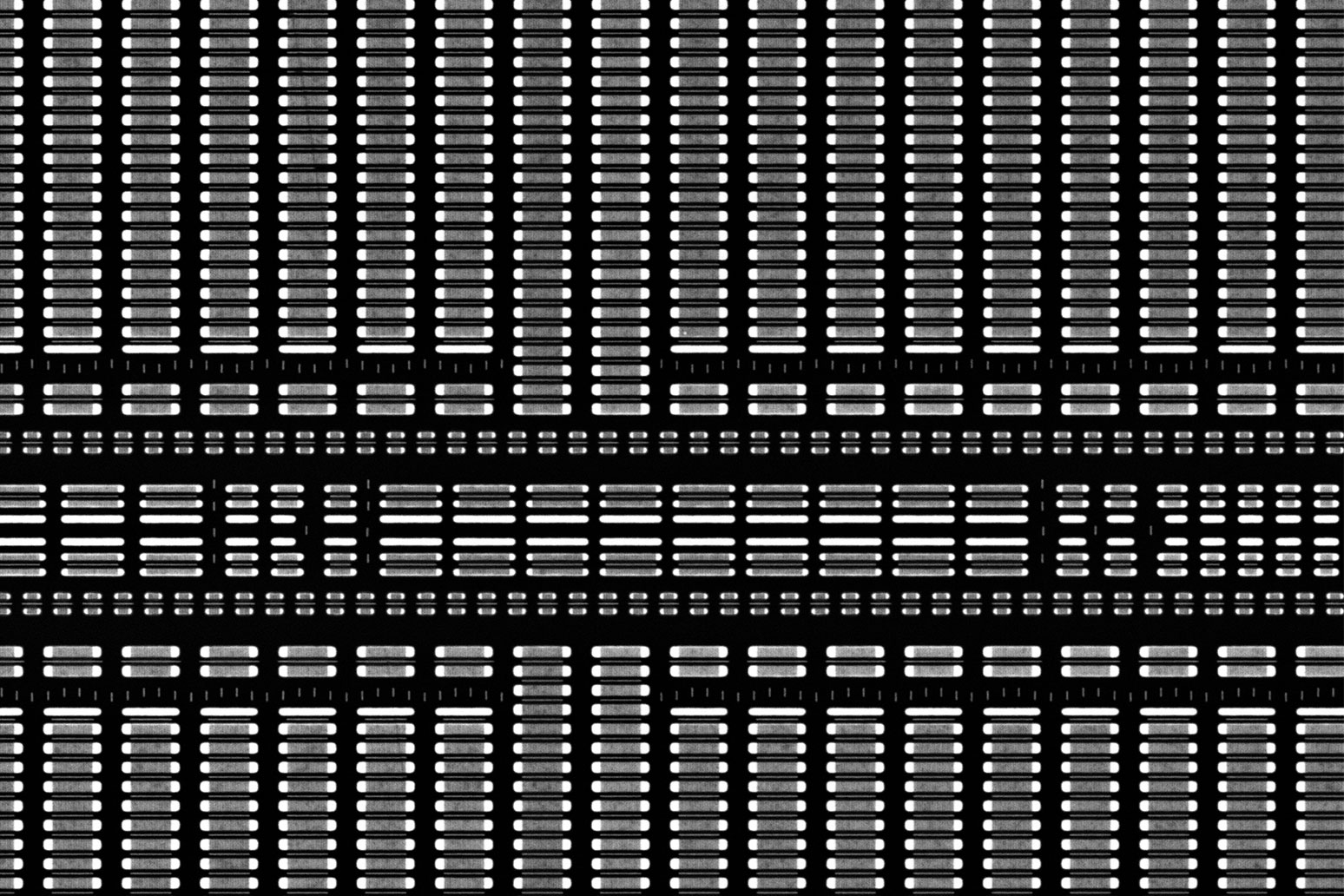

Auf Grundlage unserer Forschungsarbeiten bieten wir nicht nur Analysen auf Systemebene an, sondern auch vertiefende Untersuchungen elektronischer Bauteile. Mit modernsten, aus unseren Forschungsergebnissen hervorgegangenen Tools prüfen wir Einzelkomponenten auf Zuverlässigkeit, Originalität, mögliche IP-Verletzungen sowie auf Fehlerursachen. Die gewonnenen Erkenntnisse tragen dazu bei, Produkte gezielt zu optimieren, Schwachstellen frühzeitig zu erkennen und elektronische Systeme robuster und manipulationssicherer auszulegen. Unser nach Common Criteria – Evaluation Assurance Level 6 (CC-EAL6) zertifiziertes Sicherheitslabor ermöglicht zudem die wissenschaftliche Untersuchung sicherheitsrelevanter Bausteine. Durch eine vollflächige planare Präparation der Metalllagen eines IC und den anschließenden Chipscan können wir mithilfe einer GDSII-Konversion Hinweise auf IP-Verletzungen sowie Verdachtsmomente für manipulative Eingriffe in die Schaltung identifizieren.

Fehleranalyse und Authentizitätsprüfung auf Package- & Chiplevel

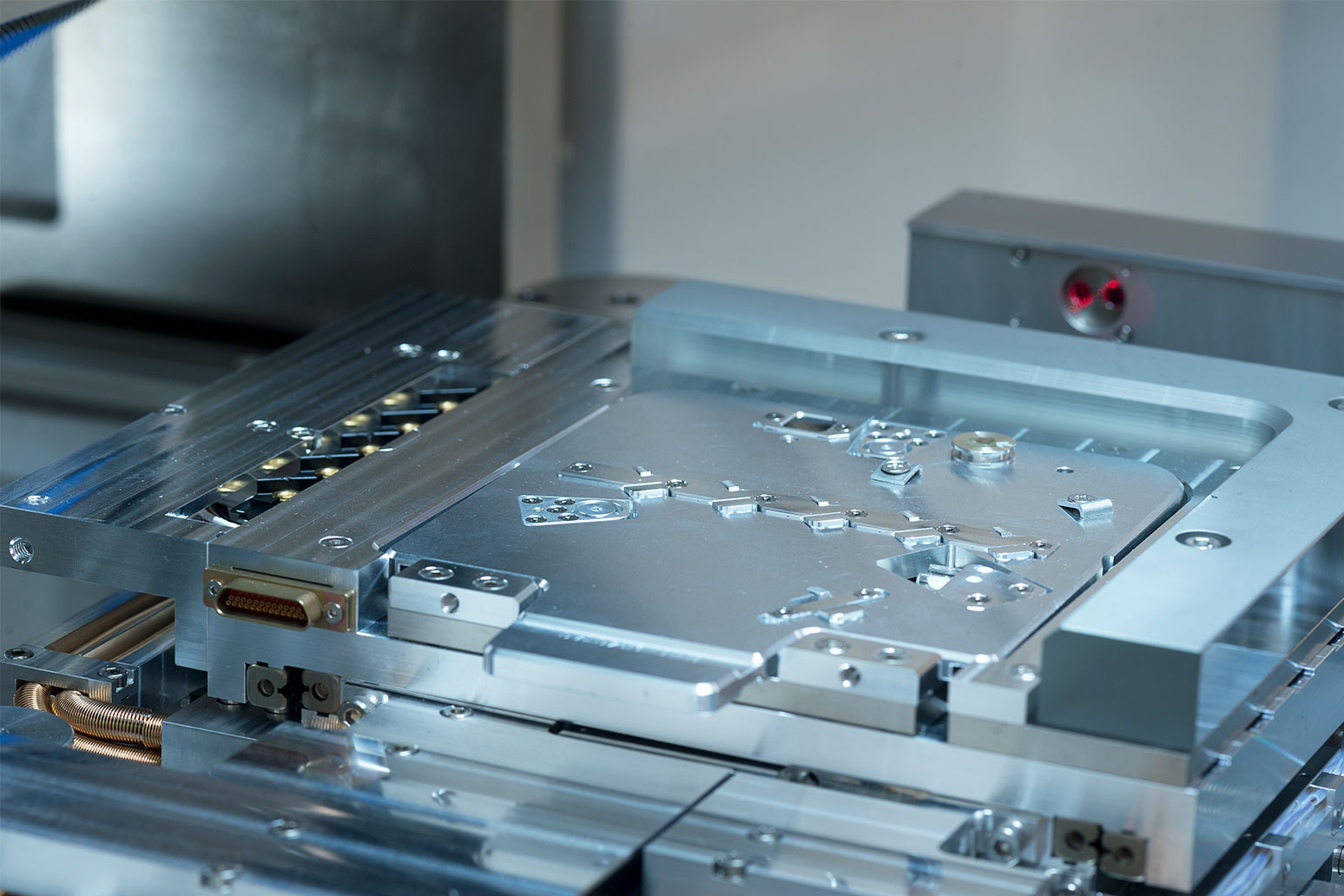

Ansicht der Raith Velion FIB-SEM bei geöffnetem Front Cover

Package- & Chiplevel-Analysen

Analysen von elektronischen Bauteilen

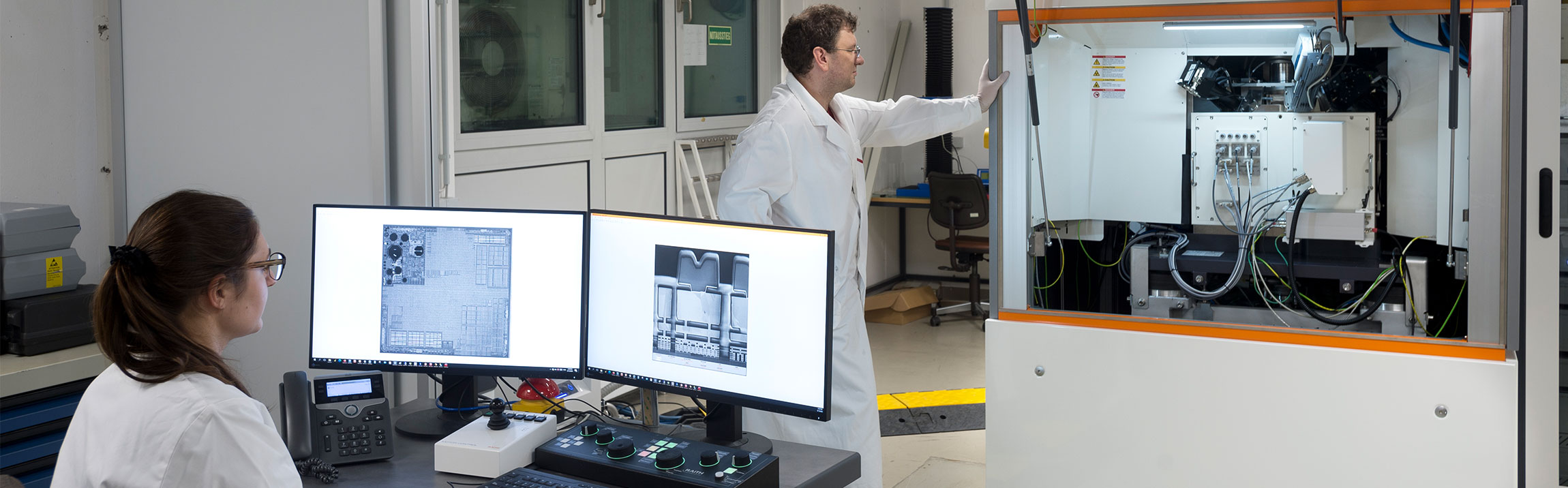

- Fehler- und Schadensanalyse mittels lichtoptischer- und Röntgeninspektion, metallografischer Schliffpräparation sowie Rasterelektronenmikroskop, sowie elektrischer Messung auf IC-Level

- Modernste Tools zur Einzelkomponentenanalyse hinsichtlich Zuverlässigkeit, Originalität, IP-Verletzung

- Sicherheitslabor zertifiziert nach Common Criteria – Evaluation Assurance Level 6 (CC-EAL6) für Untersuchung sicherheitsrelevanter Bausteine

- Vollflächige planare Präparation einzelner Metalllagen eines IC mit GDSII-Konversion und Untersuchung auf IP-Verletzung oder maligne Manipulation

- Tiefergehende Analyse zur Robustheit und ESD-Untersuchungen in Kooperation mit der Expertengruppe der elektrischen Messtechnik

Analysen auf Komponentenlevel

- Elektrische Charakterisierung von SMD Komponenenten

- Originalitätsprüfung von IC und Packages

- IC-Technologieanalyse

- De-Packaging

- De-Prozessierung von IC: von aktiver Seite (De-Layering) oder rückseitig (Chipdünnen)

- Vollflächige Rasterelektronenmikroskopie-Aufnahme ganzer Metallisierungslagen und deren Präparation

- Patentanalyse

BSI-Standortzertifizierung des Fraunhofer EMFT

Informationen zu Umfang, Ergebnissen und Status der BSI-Standortzertifizierung.

Eintrag mit Status, Gültigkeit und zugehörigen Zertifikatsdokumenten - BSI Standortzertifizierung - Fraunhofer EMFT

Prüf- und Zertifizierungsbericht des BSI zur IT-Sicherheit des Standorts - BSI Site Certification Report - Fraunhofer EMFT

Umfang und Maßnahmen der BSI-Standortzertifizierung - BSI Site Security Target Lite - Fraunhofer EMFT

Tiefergehende Analysen hinsichtlich Robustheit und ESD-Untersuchungen bieten wir in enger Kooperation mit unserer Expertengruppe der elektrischen Messtechnik an.

Sie wollen mehr über Package- & Chiplevel-Analysen in der Praxis erfahren?

Dann nehmen Sie mit uns Kontakt auf!