Die Vielzahl der Anwendungsfälle für Edge AI stellt eine breite Palette von Anforderungen an Edge-AI-Prozessoren. Allzweckprozessoren sind für Hochleistungsaufgaben nicht geeignet, und viele Anwendungsfälle haben nicht das erforderliche Volumen, um anwendungsspezifische Prozessoren kommerziell rentabel zu machen. SENNA wurde entwickelt, um genau diese Herausforderung zu bewältigen, indem es eine auf Spiking Neural Networks (SNN) basierende Verarbeitung für Anwendungen mit extrem geringer Latenz und geringem Stromverbrauch ermöglicht und gleichzeitig eine FPGA-ähnliche Vielseitigkeit bietet.

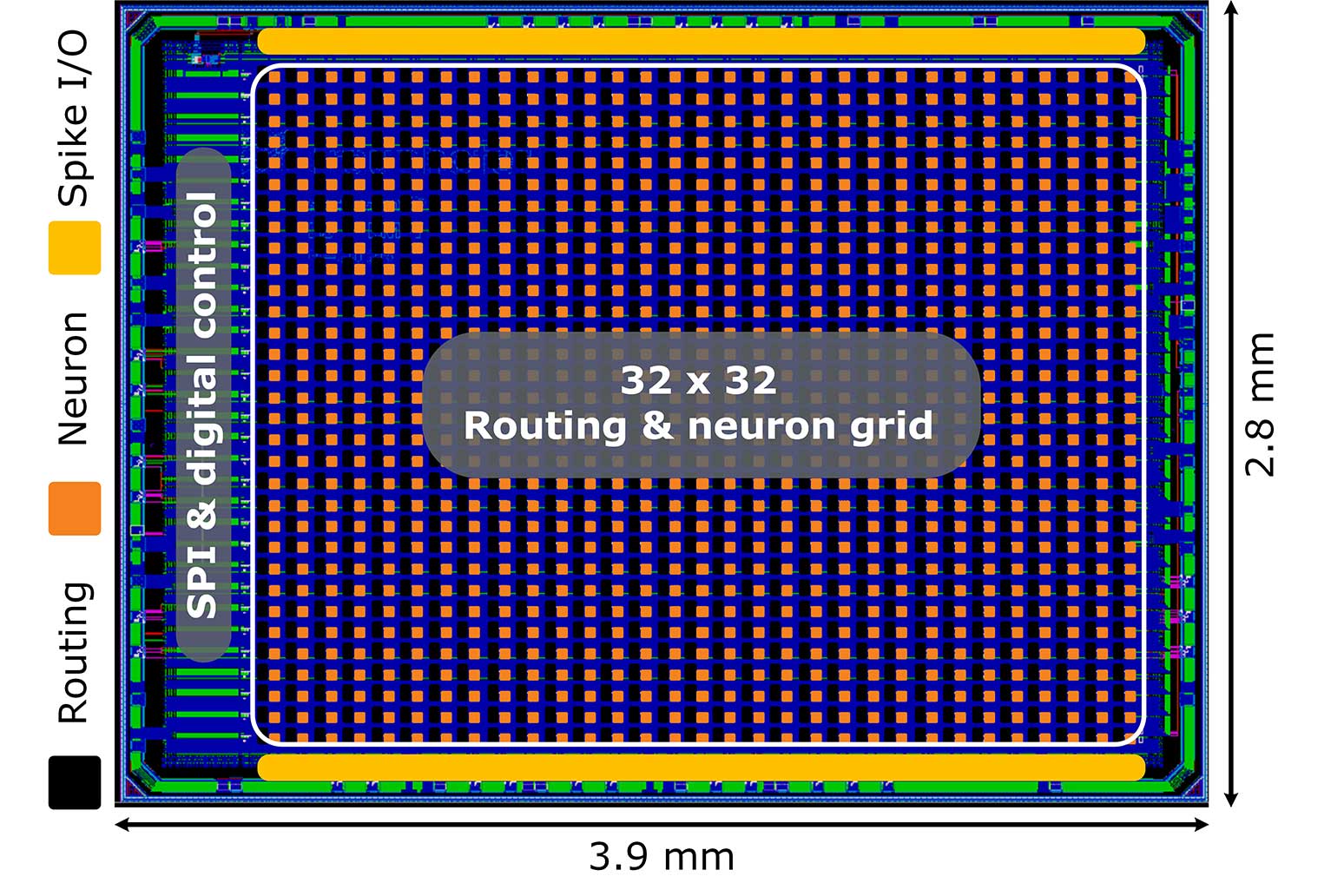

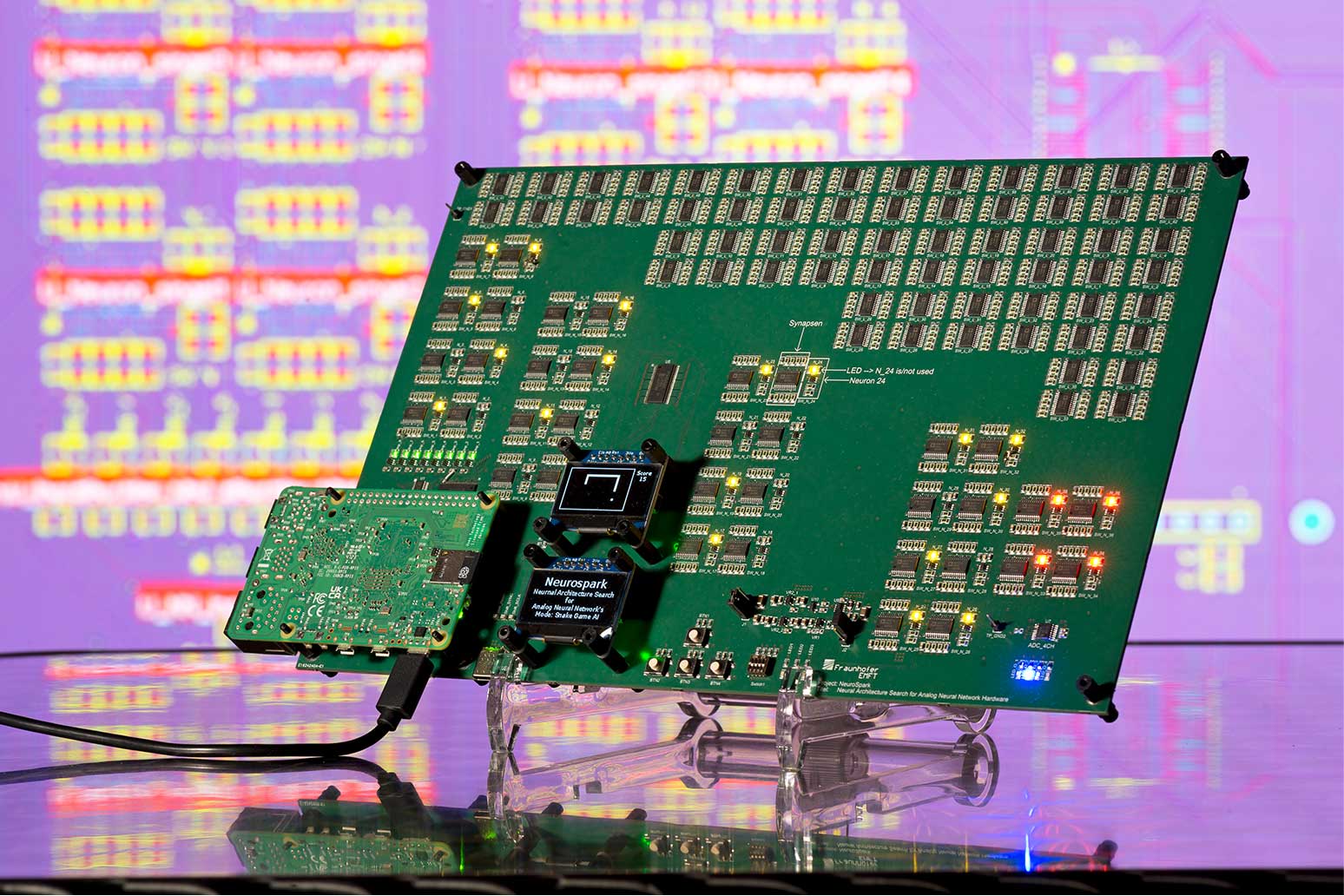

SENNA ist ein programmierbarer neuromorpher Prozessor, der auf einem Mixed-Signal, Circuit-Switched Field-Programmable Spiking Neuron Array (FPSNA) basiert. Er verarbeitet Spikes nativ mit vollständig parallelen Neuronen-Updates und direkter Spike-Eingabe/-Ausgabe und ermöglicht so ereignisbasierte, zeitdeterministische Inferenz bei extrem geringer Latenz und geringem Stromverbrauch. SENNA wurde in enger Zusammenarbeit zwischen Fraunhofer EMFT und Fraunhofer IIS entwickelt.

Edge AI neu denken: Pulsierende neuronale Netze mit SENNA

Unsere Vision: Kontinuierliche Edge-AI-Pipelines

Herkömmliche Edge-Pipelines digitalisieren analoge Signale, puffern sie und verarbeiten zeitdiskrete Batches, die vom tatsächlichen Signal-Timing losgelöst sind. Mit SENNA überdenken wir diesen Ablauf von Anfang bis Ende:

- Analoge Merkmalsextraktion in kontinuierlicher Zeit: Ein neuromorphes Frontend am Sensor führt die Merkmalsextraktion direkt an der analogen Wellenform (z. B. Nulldurchgänge, Hüllkurven, spektrale oder zeitliche Informationen) durch, ohne starre Abtastpläne vorzugeben.

- Spike-Kodierung: Nur markante Merkmale werden in Spikes kodiert, wobei die zeitliche Struktur und Spärlichkeit erhalten bleiben.

- Kontinuierliche Spike-Berechnung: Das FPSNA von SENNA verarbeitet Spikes bei ihrem Eintreffen vollständig parallel und ohne Paketweiterleitungsaufwand, was zu einer vorhersehbaren, begrenzten und minimalen Verzögerung im Netzwerk führt.

- Ansteuerung ohne Umwege: Ausgangs-Spikes können direkt Aktor-Treiber ansteuern oder Interrupt-Leitungen für Überwachungsprozessoren (z. B. in Robotern) auslösen, wodurch der Regelkreis mit deterministischem Timing geschlossen wird.

Warum neuromorphe Frontends?

Die Gesamteffizienz und Reaktionsfähigkeit eines Spike-Systems hängen entscheidend davon ab, was der Prozessor berechnen soll. Die Darstellung aller Rohsignalinhalte für SENNA verschwendet Energie und Latenzbudget. Stattdessen sollte das Frontend:

- Nur aufgabenrelevante Merkmale (anwendungs- und sensorspezifisch) extrahieren.

- Diese als Impulse codieren, um zeitliche Hinweise und Sparsamkeit zu bewahren.

- Die Kodierung an die SNN-Topologie anpassen, damit das Netzwerk den besten Kompromiss zwischen Leistung und Energieverbrauch auf SENNA erzielt.

Solche neuromorphen Frontends sind eine Voraussetzung für die zeitkontinuierliche Verarbeitung von Sensordaten mit extrem geringer Latenz.

Hardware–Software Co-Design auf FPSNA

Das Design solcher Frontends ist eine Herausforderung sowohl für die Schaltung als auch für das System. Es erfordert die gemeinsame Optimierung der analogen Merkmalsextraktion (Rauschen, Linearität, Dynamikbereich, Bandbreite), der Spike-Kodierung (Schwellenwert, adaptive Verstärkung/Abklingzeit, Refraktärzeit) und des nachgeschalteten SNN-Modells. Wir betrachten dies als ein Hardware-Software-Co-Design-Problem, einschließlich hardware-bewusstem oder hardware-in-the-loop-Training und expliziter End-to-End-Latenzbudgetierung. Wir untersuchen, wie FPSNA-Ressourcen und -Routing organisiert werden sollten, um die SNN-Topologien zu unterstützen, die für Folgendes erforderlich sind:

- Intelligente Signalverarbeitung (z. B. Kommunikations-PHY-Anpassung, Beamforming-Primitive)

- Regelkreise (Feedbackschleifen mit extrem geringer Latenz)

- Anomalie Erkennung (Streaming-Änderungs- und Neuheitserkennung)

- Akustische RADAR (ADAR)-Frontends (time-of-flight, Doppler, Mikro-Doppler)

Fraunhofer EMFT für Sensorsysteme der nächsten Generation

Mit diesen Funktionen steht SENNA als zeitkontinuierlicher, zeitdeterministischer Prozessor direkt an der Schnittstelle zwischen Sensoren und Aktoren. Dies steht im Einklang mit der Mission des Fraunhofer EMFT, Sensor- und Aktorsysteme für Mensch und Umwelt zu entwickeln. Die geringe Latenz und die hohe zeitliche Auflösung passen auch gut zu unseren Stärken im Bereich des Schaltungsdesigns für Ultraschall und HF, wo Timing-Genauigkeit und Phasenkohärenz von größter Bedeutung sind. Das Schaltungsdesign-Team des Fraunhofer EMFT trägt mit folgenden Aktivitäten zur Entwicklung von SENNA bei:

- Neuromorphe Frontends für Sensoren

- Analoge Merkmalsextraktion in Sensornähe (kontinuierliche Zeitumhüllungen, Filter, Ereignisdetektoren)

- Auf das nachgeschaltete SNN zugeschnittene Spike-Codierungsschaltungen (Schwellenwertbildung, adaptive Dynamik, Dynamikbereichssteuerung)

- Kointegration mit Sensorschnittstellen (einschließlich Hochspannungs-MEMS-Treibern, rauscharmen analogen Frontends)

- Hardware-Software-Co-Design für SENNA

- Gemeinsame Optimierung von Codierungsschemata, SNN-Topologie und FPSNA-Platzierung/Routing unter Berücksichtigung von Latenz- und Energiebudgets

- Hardwarebewusstes Training und Hardware-in-the-Loop-Validierung für robuste Timing- und Variabilitätsbedingungen in der Praxis

- Systemintegration an der Grenze zwischen Sensor und Aktuator

- Deterministische Sensor-Aktuator-Schleifen mit minimaler Verzögerung

- Erforschung von Schnittstellen zu Ultraschall- und HF-Systemen, bei denen eine hohe zeitliche Auflösung unerlässlich ist

- Interrupt- und Treiber-Schnittstellen für eingebettete Steuerungen und Robotersysteme

Auswirkungen und Anwendungen

In missionskritischen Anwendungen können selbst kleinste Verzögerungen erhebliche Sicherheitsrisiken oder finanzielle Schäden verursachen. Beispielsweise in Anwendungsfällen wie medizinischen Notfällen, Geschäftstransaktionen oder zuverlässiger Kommunikation kann SENNA den entscheidenden Unterschied in Bezug auf Reaktionszeit und Effizienz ausmachen.

- Schnellere Entscheidungen an der Edge: Durch Streaming und zeitkontinuierliche Verarbeitung werden die Phasen „Abtasten – Speichern – Verarbeiten“ zu sofortigen Reaktionen zwischen Sensor und Aktor zusammengefasst.

- Energieproportionalität: Spike-gesteuerte Berechnung und analoge Vorauswahl reduzieren unnötige Arbeit an irrelevanten Signalinhalten.

- Vorhersagbares Timing: Deterministisches Spike-Routing und parallele Neuronen-Updates ermöglichen enge, überprüfbare End-to-End-Latenzbudgets.

- Domänenübergreifende Eignung: Von Closed-Loop-Steuerung und Kommunikations-PHYs bis hin zu ereignisbasierter Sensorik und ADAR zielt SENNA auf Domänen ab, in denen Timing-Garantien eine wichtige Rolle spielen.