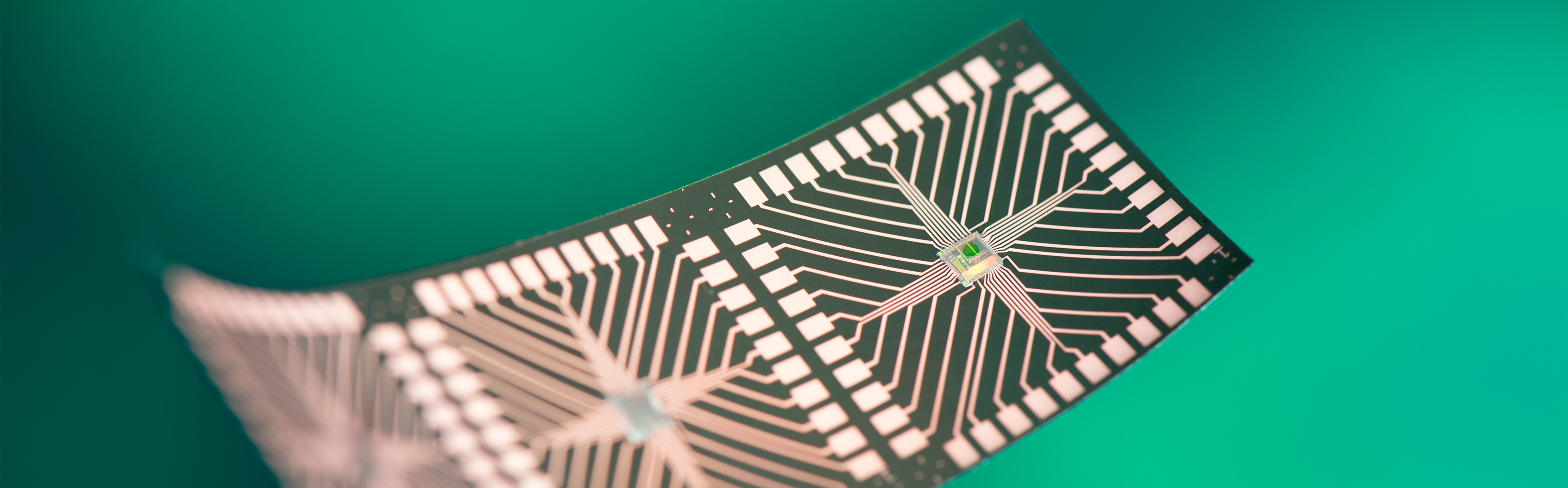

Die zuverlässige elektrische Anbindung eines integrierten Schaltkreises (IC, Integrated Circuit) an die umgebende Elektronik ist ein entscheidender Schritt bei der Chipintegration. Sie stellt eine zentrale Herausforderung für alle mikroelektronischen Systeme dar – insbesondere in Anwendungen wie Chipkarten, Sensoren oder tragbaren Geräten. Eine bewährte Lösung ist das sogenannte „Mold Package“: Dabei wird der Chip in ein Kunststoffgehäuse eingebettet und über außenliegende, lötfähige Kontakte elektrisch mit seiner Umgebung verbunden. Unser Ansatz geht darüber hinaus: Wir entwickeln sehr dünne und flexible Chip-Folien-Packages.

Elektrische Kontaktierung als Schlüssel zur Chipintegration

Wie integrierte Schaltkreise zuverlässig mit ihrer Umgebung verbunden werden

Die Forschung am Fraunhofer EMFT konzentriert sich auf drei zukunftsweisende Ansätze für das Chip-Assembly:

- Chip-on-Film (CoF) bzw. sogenannte Thin-Chip-Foil Packages

- Chiplet-Integration

- Chip-Assembly für Quantencomputing

Vorteile der folienbasierten Chipintegration

Die Integration und elektrische Anbindung von IC-Bausteinen auf flexiblen Folien ist bereits in Anwendungen wie Chipkarten etabliert. Mit den innovativen Ansätzen vom Fraunhofer EMFT erschließen sich jedoch ganz neue Möglichkeiten in der Rolle-zu-Rolle (R2R) Fertigung – für kostengünstige, skalierbare und nachhaltige Elektroniklösungen. Unsere langjährige Kompetenz umfasst die Herstellung, Handhabung und Charakterisierung ultradünner Silizium-Bauelemente sowie die Erzeugung hochauflösender Kupferleiterbahnen (< 30 µm) auf Polyimid-Folien.

Forschungsziel: Thin Chip Foil Packages "Made in Europe"

Ein zentrales Ziel unserer Forschung ist die Entwicklung von sogenannten „Thin Chip Foil Packages“ im Rolle-zu-Rolle-Verfahren. Diese Technologie eröffnet neue Wege für das Hochdurchsatz-Packaging, insbesondere für flexible und großflächige Elektronikanwendungen. Dabei legen wir Wert auf Prozesssicherheit, Präzision und europäische Wertschöpfung.

Anwendung: Innovationen für Chiplet-Systeme und Quantencomputing

Unsere neuesten Forschungsprojekte konzentrieren sich auf Integrationstechnologien für zukünftige Chiplet-Systeme (z. B. im Rahmen von APECS oder der Heterointegration). Hier entwickeln wir fortschrittliche Lösungen für das Assemblieren auf Glas-Interposern (mit TGV-Technologie) sowie für die Heterointegration mit Folien-Substraten wie Polyimidfolie. Ein besonderer Fokus gilt hochfrequenztauglichen Chip-Systemen (RF-on-Flex) für Anwendungen in flexiblen Antennen und 360°-RADAR-Systemen.

Auch im Bereich Quantencomputing sind innovative Lösungen gefragt: Neue Packaging- und Integrationstechnologien ermöglichen die Verbindung zahlreicher ICs auf gemeinsamen Interposern – häufig unter den anspruchsvollen Bedingungen der Supraleitfähigkeit und mit extrem hoher Präzision (< 0,5 µm).