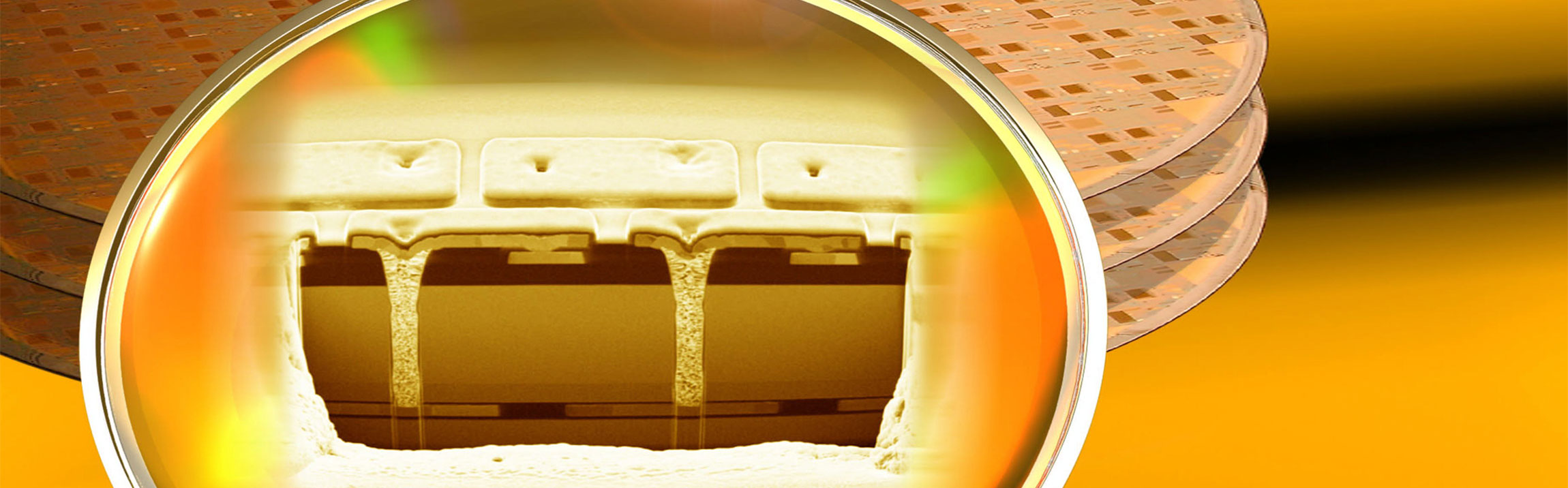

Am Fraunhofer EMFT liegt ein zentraler Fokus unserer Aktivitäten im Bereich der Mikrosystemintegration auf der heterogenen 3D-Integration. Dieser zukunftsweisende Ansatz ermöglicht kompakte, leistungsfähige und multifunktionale System-on-Chip- und System-in-Package-Lösungen. Unsere 3D-Integrationsplattform ist durch zahlreiche Patente auf wesentliche Prozessschritte, Materialien und Systemarchitekturen geschützt. Dadurch bieten wir eine technologisch führende und IP-sichere Basis für den industriellen Einsatz. Die Integrationstechnologie verbindet CMOS-kompatible Elektronik mit MEMS-basierten Sensoren zu miniaturisierten Hochleistungssystemen. Über standardisierte Schnittstellen lassen sich diese Sensoren auslesen, steuern und in IoT-Ökosysteme verschiedenster Branchen einbinden.

Heterogene 3D Integration

Patentierte Lösungen des Fraunhofer EMFT für KI, IoT, 5G und Quantentechnologien

Anwendungsfelder der heterogenen 3D Integration

Die heterogene 3D-Integration ist längst mehr als ein Forschungsfeld – sie treibt bereits heute zahlreiche Geräte und Systeme an. Anwendungen mit hohen Stückzahlen wie 3D-gestapelte Bildsensoren und 3D-Speicherchips sind zentrale Komponenten moderner Mobilgeräte und Dateninfrastrukturen.

Darauf aufbauend unterstützt das Fraunhofer EMFT die Industrie bei der Entwicklung von Chiplet-Lösungen und System-in-Package (SiP)-Konzepten für eine Vielzahl zukunftsrelevanter Einsatzgebiete, darunter:

- Künstliche Intelligenz (KI) und Maschinelles Lernen (ML)

- IoT und Edge Computing

- Kommunikationstechnologien jenseits von 5G / 6G

- High-Performance Computing (HPC)

- Fortschrittliche Sensor- und Embedded-Systeme

- Automatisierungsprozesse in der Forschung und Medizin

- Quantentechnologien, wie supraleitende oder Ionenfallen-basierte Quantencomputer

3D Integration – einsatzbereite Technologien für die Praxis

Das Fraunhofer EMFT bietet Zugang zu modernsten Prozesstechnologien – darunter Solid-Liquid-Interdiffusion (SLID)-Bonden sowie ZiBond®, eine Waferbonding-Technologie bei niedrigen Temperaturen (ca. 200 °C), die eine zuverlässige, skalierbare Systemintegration auch für temperaturempfindliche Komponenten ermöglicht.

Die zentralen Vorteile unserer Integrationsverfahren im Überblick:

- Hochdichte vertiakel Verbindungen mit "Pitches" bis herab zu 5 μm

- Kosteneffiziente Herstellung durch TSV-freie Architekturen

- Mechanische und elektrische Verbindungen in einem Prozessschritt

- CMOS- und MEMS-Co-Integration auf Wafer- und Chip-Ebene

Mit diesen Kompetenzen ermöglichen wir unseren Partnern die Realisierung ultra-kompakter, leistungsstarker mikroelektronischer Systeme – anwendungsspezifisch zugeschnitten und bereit für die industrielle Fertigung.