Presseinformation

Quantencomputing in neuen Dimensionen: Auf dem Weg zu skalierbarer supraleitender Quanten-Hardware

Die Entwicklung und Charakterisierung von skalierbarer Quanten-Hardware ist ein Schlüsselfaktor, um Quantencomputing in reale Anwendungen zu bringen. Forscherinnen und Forscher des Fraunhofer EMFT arbeiten an innovativen Ansätzen, um die Skalierung voranzutreiben. Auf der diesjährigen World of Quantum vom 24. bis 27. Juni in München präsentieren wir mehrere Demonstratoren aus unserem Quantentechnologie-Programm, in dem wir wissenschaftliche Exzellenz und technische Expertise vereinen.

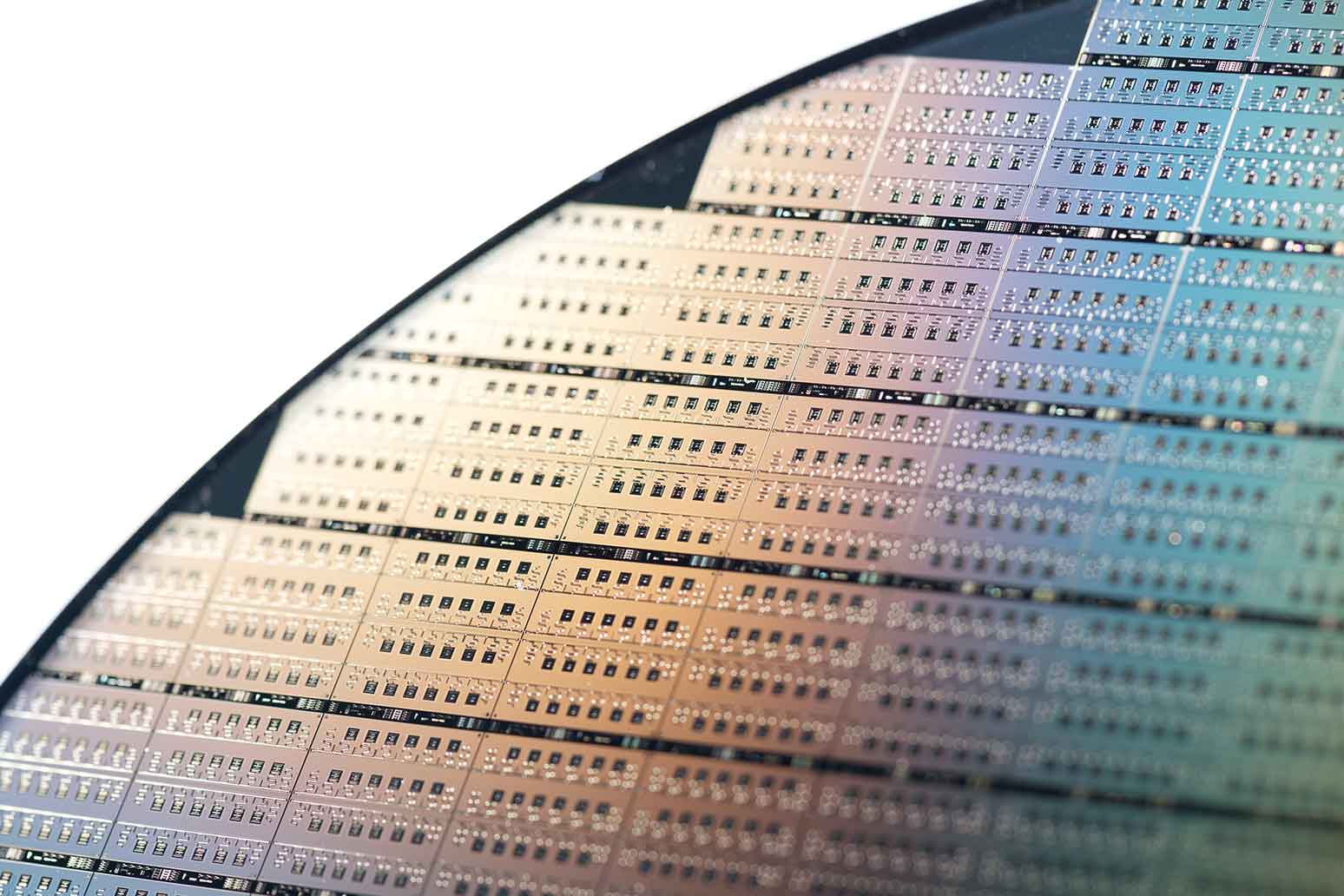

Erstmalig präsentieren wir einen 200 mm Silizium-Wafer mit Qubit-Chips, die in der Pilotlinie des Fraunhofer EMFT hergestellt wurden. Das Layout umfasst einen Qubit-Testchip mit vier Festfrequenz-Qubits, die bei 4 - 5 GHz arbeiten, sowie koplanare Wellenleiterresonatoren. Die aktuellen Leistungsdaten zeigen mittlere Relaxationszeiten T1 um 100 μs, wobei einige Bauelemente T1-Werte von ca. 200 μs erreichen - die höchsten bisher berichteten Energie-Relaxationszeiten weltweit für supraleitende Qubits, die mit subtraktiven, industrietauglichen Methoden auf großen Wafern hergestellt wurden! Die Langzeitüberwachung über 16 Stunden hat eine gleichbleibend gute Leistung gezeigt und unterstreicht die Zuverlässigkeit derTechnologie.

Flexible Lösungen für komplexe Herausforderungen

Da supraleitende Quantensysteme immer komplexer werden, ist es von entscheidender Bedeutung, ihren Platzbedarf zu minimieren und gleichzeitig die Leistungsfähigkeit zu erhalten. Auf der World of Quantum stellen wir einen Technologiedemonstrator für flexiblesupraleitende Mehrkanalverbindungen vor, die für die Übertragung von Steuer- und Datensignalen zwischen Millikelvin (mK) und 4 K-Stufen konzipiert sind. Unsere Lösung bietet eine hohe Signaldichte, eine geringe aktive Wärmeabgabe und einen begrenzten passiven Wärmetransfer, was sie ideal für kryogene Anwendungen macht. Die Verbindungen weisen extra lange Leitungen auf, die von Zentimetern bis zu Metern reichen, und bieten eine alternative Methode für die Verbindung von hochdichten Wellenleitern mit gedruckten Schaltungen (PCBs).

Fortschrittliche Flip-Chip-Technologie mit Indium-Mikro-Bumps

Erweiterte Flip-Chip-Technologie ist für Quantencomputing aus mehreren Gründen entscheidend. Sie ermöglicht beispielsweise die Weiterleitung von Signalen zur Steuerung und zum Auslesen von Qubits und verbessert die Leistung der Qubits durch Verringerung des Übersprechens, was für zuverlässige Quantenoperationen unerlässlich ist. Darüber hinaus sorgt die Technologie für ein optimiertes Wärmemanagement, da Mikrobumps eine effiziente Wärmeübertragung ermöglichen. Wir stellen 3DBaugruppen vor, die auf 200-mm-Siliziumwafern entwickelt und hergestellt wurden, um die Flip-Chip-Technologie weiterzuentwickeln. Der Testaufbau umfasst einen Qubit- Chip mit 24 schwebenden Qubits und einen Trägerchip mit Siliziumpfeilern, die mit Indium beschichtet sind und als Mikrobumps im Flip-Chip-Aufbau fungieren.

Ausblick

Das Fraunhofer EMFT arbeitet kontinuierlich weiter an Lösungen zur Skalierung von Quantencomputern, insbesondere zur Entwicklung industrietauglicher Fertigungstechniken für Quantenhardware. Mit unserer Pilotlinie wollen wir eine Foundry-ähnliche Fertigung von Kleinserien und Prototypen für Anwendungen der Quantentechnologie etablieren, z.B. QPUs, QT-Geräte, QT-Sensorik, kundenspezifische QT-Prozesse.

Besuchen Sie uns!

Erfahren Sie mehr über unser F&E-Portfolio und besuchen Sie unseren Stand A1.222 im Munich Quantum Valley space! Nutzen Sie die Gelegenheit, mit unseren Experten zu diskutieren und die neuesten Entwicklungen kennenzulernen, die den Weg für reale Quantenanwendungen ebnen.

Presseinformation zum Download

Letzte Änderung: